# AN ANALYSIS OF MULTICORE CPUS AND ACCELERATORS' HARDWARE AWARENESS AND HETEROGENEOUS COMPUTING

#### **Abdul Rasheed A**

Lecturer in Electronics Engineering Government Residential Women's Polytechnic College Payyanur - 670307 Kannur (Dt.), Kerala

# ABSTRACT

A computer procedure known as heterogeneous multi-processing involves more than one connected and active processor at once. Performance is improved by the multi-core technology, which also adds specialized processing power to handle specific tasks. The parallel computing ecosystem has seen significant and extremely dynamic developments in recent years. For scientific and commercial applications, the paradigm shift toward multicore and many core technologies, along with accelerators in a heterogeneous environment, offers a significant amount of computing capacity. However, comprehensive approaches linking the knowledge of hardware architecture, software design, and numerical algorithms are urgently required if one is to fully benefit from these new technologies. Multiple cores in homogeneous multicore systems all have the same architecture and microarchitecture. The Arm quad-core Cortex-A53 system serves as an illustration of this; each core in this system is identical. Two or more cores in heterogeneous multicore systems have different architectures or microarchitectures. In this paper, we provide an overview of both established and developing multicore and many core technologies, as well as accelerator concepts, from the perspective of numerical simulation and applications. The difficulties of high-performance heterogeneous computing are highlighted, and the interfaces required to bridge the gap between the hardware design and the implementation of effective numerical algorithms are discussed. A system that uses multiple types of computing cores, such as CPU, GPU, DPU, VPU, FPGA, or ASIC, is referred to as heterogeneous computing. Performance and energy efficiency can be greatly increased by allocating different tasks to specialized processors designed for a variety of uses.

*Keywords: Multi core processors; accelerators; heterogeneity; hardware-aware computing; performance optimization; parallel programming; numerical simulation.*

# **INTRODUCTION**

In the context of computing, heterogeneity typically refers to different instruction-set architectures (ISA), not just different microarchitectures (floating point number processing is an

#### **BHARAT PUBLICATION**

#### http://bharatpublication.com/current-issue.php?jID=29/IJAE

exception to this but is not typically referred to as heterogeneous), where the main processor has one and other processors have another, typically a very different architecture (possibly more than one). In the past heterogeneous figuring implied different ISAs must be dealt with in an unexpected way, while in a cutting edge model, Heterogeneous System Architecture [2] wipe out the distinction (for the client) while utilizing various processor types (ordinarily computer chips and GPUs), normally on a similar coordinated circuit, to give the best case scenario: general GPU handling (aside from the GPU's notable 3D illustrations delivering capacities, it can likewise perform numerically concentrated calculations on extremely enormous informational collections), while computer chips can run the working framework and perform customary sequential undertakings.[5]

The degree of heterogeneity in present day figuring frameworks is slowly expanding as additional scaling of manufacture innovations takes into consideration previously discrete parts to become incorporated pieces of a framework on-chip, or SoC.[6] For instance, numerous new processors currently incorporate underlying rationale for interacting with different gadgets (SATA, PCI, Ethernet, USB, RFID, radios, UARTs, and memory regulators), as well as programmable useful units and equipment gas pedals (GPUs, cryptography co-processors, programmable organization processors, A/V encoders/decoders, and so on.).[5]

Late discoveries show that a heterogeneous-ISA chip multiprocessor that takes advantage of variety presented by numerous ISAs can beat the best same-ISA homogeneous design by as much as 21% with 23% energy reserve funds and a decrease of 32% in Energy Defer Item (EDP).[3] AMD's 2014 declaration on its pin-viable ARM and x86 SoCs, codename Undertaking Sky bridge,[4] proposed a heterogeneous-ISA (ARM+x86) chip multiprocessor really taking shape.

# **HETEROGENEOUS CPU TOPOLOGY**

A framework with heterogeneous central processor geography is a framework where a similar ISA is utilized, but the actual centers are different in speed. The arrangement is more like a symmetric multiprocessor. (Albeit such frameworks are in fact topsy-turvy multiprocessors, the centers don't vary in jobs or gadget access.) There are normally two sorts of centers: a better exhibition center, typically known as the "huge" or P-center, and a more powerful center, generally known as the "little" or E-center. The terms P- and E-centers are typically utilized according to Intel's execution of heterogeneous figuring, while the terms huge and little centers are generally utilized comparable to the ARM design.[6]

A typical utilization of such geography is to improve power proficiency, particularly in portable SoCs.

#### **International Journal of Advanced Engineering**

Vol. 1, Issue IV, Jul-Sep, 2018

- ARM large. LITTLE (prevailed by Dynamic level of intelligence) is the prototypical case, where quicker high-power centers are joined with low-power centers.

- Intel has likewise created half and half x86-64 chips codenamed Lakefield, albeit not without significant constraints in guidance set help. The fresher Birch Lake decreases the penance by adding more guidance set help to the "little" center.

# UNDERSTANDING MULTI CORE PROCESSORS AND SYSTEMS[12]

Multi center processors and frameworks use focal handling units (computer chip) which have at least two unmistakable implanted handling components.

These gadgets are regularly chosen to diminish cost, increment framework execution and decrease generally power utilization.

There are three essential sorts of multi center setups: Fringe, Homogeneous and Heterogeneous.

The "Fringe" setup is really a semi multi center in that there is ordinarily a solitary focal handling center with various related equipment gas pedal blocks around it. The computer processor centers as well as the peripherals are on a similar piece of silicon, as opposed to as discrete parts on a board.

The peripherals are committed to explicit assignments and used to offload the central processor center. These equipment gas pedals might incorporate cryptography motors, memory the executives, information capacity the board (e.g., Strike usefulness for information equality and appropriation), design matching motors and graphical handling units (GPU).

In a "Homogeneous" multi center, a similar kind of central processor is imitated on various occasions on a solitary chip. Every computer chip has the very same highlights, memory structure and inner transport structure. The central processor may likewise contain equipment gas pedal blocks for memory the executives or numerical calculations.[5]

A homogeneous setup is best utilized for broadly useful handling where parallelism can be utilized to build execution and figuring power. A homogeneous framework will likewise have extra equipment gas pedal chips for application explicit necessities like designs.

A "Heterogeneous" multi center gadget is a cross breed of the Fringe and the Homogeneous designs. These chips can incorporate various same, comparative, or various sorts of processors as well as products of every equipment gas pedal. A heterogeneous multi center is more application explicit as its motors are chosen to enhance execution and decrease power specifically undertakings.

#### http://bharatpublication.com/current-issue.php?jID=29/IJAE

Related with all of the handling centers and equipment gas pedal motors is a transport connecting everything together. As there are numerous gadgets which might have to speak with each other, as well as to approach shared on-chip assets and to convey off chip - a switch texture transport is generally reasonable for multi center gadgets. This differentiations with a common transport engineering which can be utilized inside a solitary computer processor and fringe type framework.[13]

In all superior execution multi center plans, the transport texture is non-hindering which permits all components to have free admittance to all assets. In some multi center gadgets, it is important to have upwards of 32 transport aces working simultaneously to guarantee the information and correspondences stream un-blocked.

Writing computer programs is presumably the most difficult errand in a multi center framework. Multi stringing is utilized for the most productive dispersion of errands across the equipment centers, and to not unduly trouble the product.[12]

In a solitary center, the central processor might have to get to assets like memory reserve, peripherals, UARTs, Ethernet encoders or a showcase. In this present circumstance there is no contest for the inward transport or different motors. In any event, when there are simultaneous gets to and there are numerous strings running, there is just a single interest for each single asset which is then opened up for next string.

With at least two centers, each center can all the while have a string pushing for admittance to the asset and the asset should give information to every one of the centers. The issue becomes how to control how the asset gives information to the specific string in an impromptu design with the goal that the program can get to the information in an organized style. On the off chance that projects are running successively, a technique is expected to connect the information with the right piece of the string.14]

# CHALLENGES

Heterogeneous figuring frameworks present new difficulties not found in common homogeneous systems.[7] The presence of different handling components raises each of the issues engaged with homogeneous equal handling frameworks, while the degree of heterogeneity in the framework can present non-consistency in framework advancement, programming practices, and generally speaking framework capacity. Areas of heterogeneity can include:[8]

Vol. 1, Issue IV, Jul-Sep, 2018 <u>http://bharatpublication.com/current-issue.php?jID=29/IJAE</u>

## ISA or guidance set design

Register components might have different guidance set structures, prompting double contradiction.

## ABI or application double point of interaction

Process components might decipher memory in various ways.[9] This might incorporate both endianness, calling show, and memory design, and relies upon both the engineering and compiler being utilized.

## Programming interface or application programming connection point

Library and operating system administrations may not be consistently accessible to all figure elements.[10]

## Low-Level Execution of Language Elements

Language highlights, for example, works and strings are in many cases executed utilizing capability pointers, a system which requires extra interpretation or deliberation when utilized in heterogeneous conditions.

## Memory Point of interaction and Order

Process components might have different store structures, reserve coherency conventions, and memory access might be uniform or non-uniform memory access (NUMA). Contrasts can likewise be tracked down in the capacity to peruse erratic information lengths as certain processors/units can perform byte-, word-, or burst accesses.[11]

### Interconnect

Process components might have contrasting kinds of interconnect beside fundamental memory/transport interfaces. This might incorporate devoted network interfaces, Direct memory access (DMA) gadgets, letter drops, FIFOs, and scratchpad recollections, and so on. Moreover, certain parts of a heterogeneous framework might be reserve sound, while others might require express programming inclusion for keeping up with consistency and coherency.[13-15]

### Execution

A heterogeneous framework might have computer processors that are indistinguishable concerning engineering, however have hidden miniature compositional contrasts that lead to different degrees of execution and power utilization. Imbalances in capacities matched with misty programming models and working framework reflections can now and again prompt execution consistency issues, particularly with blended responsibilities.[15]

#### **BHARAT PUBLICATION**

Vol. 1, Issue IV, Jul-Sep, 2018 <u>http://bharatpublication.com/current-issue.php?jID=29/IJAE</u>

## Advancement devices

Various sorts of processors would commonly require various apparatuses (editors, compilers, ...) for programming designers, which presents intricacy while dividing the application across those.[2]

## **Information Parceling**

While parceling information on homogeneous stages is frequently paltry, it has been shown that for the overall heterogeneous case, the issue is NP-Complete.[3] For little quantities of parts, ideal division that impeccably balance load and limit correspondence volume have been displayed to exist. [4]

# THE TREND OF HARDWARE

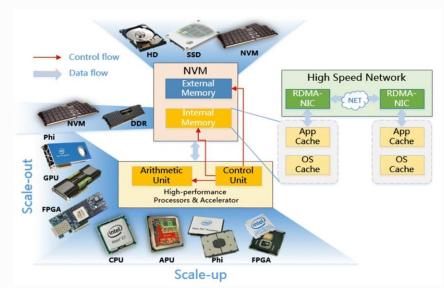

Lately, capacity, processor, and organize innovations have made an extraordinary leap forward. As displayed in Fig. 1, a developing arrangement of new equipment, engineering, and highlights are turning into the underpinning representing things to come registering stages. The latest things demonstrate that these methods are altogether changing the basic climate of conventional information the board and examination frameworks, including elite execution processors and equipment gas pedals, NVM, RDMA-competent (remote direct memory access) organizations. Altogether, the continuous basic conditions, set apart by heterogeneous multi-center engineering and mixture stockpiling order, make the generally convoluted programming configuration space become more modern [1,2,3,4].

Figure 1: The New Hardware Development Trend and the Challenges in Data Management and Analysis

# THE TREND OF PROCESSOR TECHNOLOGIES[14]

The improvement of processor innovation has gone through for over 40 years. Its advancement guide has moved from increase to scale-out, and the point decisively moves from seeking after higher clock speed and on second thought centers around making more centers per processor. As per Moore's regulation, pushing the figuring recurrence of the processor consistently is one of the main ways of working on the exhibition of the PC in the time of sequential registering. Simultaneously, loads of improvement procedures, for example, the Instruction-level parallelism, pipeline, prefetching, branch expectation, mixed up guidance execution, staggered reserve, and hyper-stringing, can be naturally recognized and used by the processor and the compiler. Subsequently, programming can reliably and straightforwardly appreciate free and normal execution gains. Nonetheless, restricted by the intensity, power utilization, guidance level parallelism, fabricating processes, and different elements, the scale-up approach arrives at the roof.[13]

After 2005, superior execution processor innovation has entered the multi-center time and multicenter equal handling innovation has turned into the standard. Yet, in spite of the fact that information handling capacity has been altogether improved in multi-center structures, programming can't naturally acquire the advantages. All things being equal, developers need to change the customary sequential projects into equal projects, and upgrade the calculation execution for the Last Level Cache of multi-center processors. These days, the exhibition of multi-center processors has been essentially improved with the semiconductor innovation. For instance, the 14-nm Xeon processor at present incorporates up to 24 centers, supporting up to 3.07 TB memory and 85 GB/s memory data transmission. Be that as it may, x86 processor actually has the drawbacks of low combination, high power utilization, and excessive cost. Likewise the universally useful multi-center processors can scarcely to satisfy the needs of the profoundly simultaneous applications. The improvement of the processor will be explicitly enhanced for an application, i.e., particular equipment gas pedals. GPU, Xeon Phi, field programmable door cluster (FPGA), and so forth are illustrative of devoted equipment gas pedals. By taking advantage of GPUs, Xeon Phi coprocessors, and FPGAs, portions of process escalated and information serious responsibility can be offloaded from the computer chip effectively. There is no question that the handling climate inside the PC framework turns out to be increasingly convoluted, and correspondingly, the information the executives and investigation frameworks could attempt to look for enhanced approaches to adjust to new circumstances effectively. [12-15]

# CONCLUSION

Heterogeneous multicore frameworks have at least two centers that contrast in engineering or micro architecture. An illustration of heterogeneous multicore frameworks is the blend of a chip

#### http://bharatpublication.com/current-issue.php?jID=29/IJAE

center with a microcontroller class center (for instance, blend of Cortex-A, Cortex-M or DSP centers). Over the most recent couple of years, the scene of equal figuring has been dependent upon significant and exceptionally unique changes. The change in outlook towards multicore and many core innovations combined with gas pedals in a heterogeneous climate is offering an extraordinary capability of registering power for logical and modern applications. Notwithstanding, for one to make the most of these new innovations, all-encompassing methodologies coupling the skills going from equipment engineering and programming plans to mathematical calculations are a squeezing need. Equal processing is not generally restricted to supercomputers and is currently considerably more differentiated, with a huge number of innovations, structures, and programming approaches prompting expanded intricacy for designers and specialists. Heterogeneous multi-handling alludes to a PC activity wherein more than one processor is associated and is dynamic simultaneously. The multi-center framework assists with execution and, furthermore, adds specific handling capacities to deal with specific assignments.

## REFERENCES

[1]. Stone, John E., et al. "Evaluation of emerging energy-efficient heterogeneous computing platforms for biomolecular and cellular simulation workloads." 2016 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW). IEEE, 2016.

[2]. Ciznicki, Milosz, Krzysztof Kurowski, and Jan Weglarz. "Energy aware scheduling model and online heuristics for stencil codes on heterogeneous computing architectures." Cluster Computing 20 (2017): 2535-2549.

[3]. Usui, Hiroyuki, et al. "DASH: Deadline-aware high-performance memory scheduler for heterogeneous systems with hardware accelerators." ACM Transactions on Architecture and Code Optimization (TACO) 12.4 (2016): 1-28.

[4]. Halpern, Matthew, Yuhao Zhu, and Vijay Janapa Reddi. "Mobile CPU's rise to power: Quantifying the impact of generational mobile CPU design trends on performance, energy, and user satisfaction." 2016 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2016.

[5]. Chen, Quan, et al. "Baymax: Qos awareness and increased utilization for non-preemptive accelerators in warehouse scale computers." ACM SIGPLAN Notices 51.4 (2016): 681-696.

[6]. Suriano, Leonardo, et al. "Analysis of a heterogeneous multi-core, multi-hw-acceleratorbased system designed using PREESM and SDSoC." 2017 12th International Symposium on Reconfigurable Communication-centric Systems-on-Chip (ReCoSoC). IEEE, 2017.

[7]. Wang, Chao, et al. "Reconfigurable hardware accelerators: Opportunities, trends, and challenges." arXiv preprint arXiv:1712.04771 (2017).

#### **International Journal of Advanced Engineering**

Vol. 1, Issue IV, Jul-Sep, 2018

[8]. Ayres, Daniel L., and Michael P. Cummings. "Heterogeneous hardware support in BEAGLE, a high-performance computing library for statistical phylogenetics." 2017 46th International Conference on Parallel Processing Workshops (ICPPW). IEEE, 2017.

[9]. Kreutzer, Moritz, et al. "GHOST: building blocks for high performance sparse linear algebra on heterogeneous systems." International Journal of Parallel Programming 45 (2017): 1046-1072.

[10].Memeti, Suejb, et al. "Benchmarking OpenCL, OpenACC, OpenMP, and CUDA: programming productivity, performance, and energy consumption." Proceedings of the 2017 Workshop on Adaptive Resource Management and Scheduling for Cloud Computing. 2017.

[11].da Silva, Lucas B., et al. "Exploring the dynamics of large-scale gene regulatory networks using hardware acceleration on a heterogeneous cpu-fpga platform." 2017 International Conference on ReConFigurable Computing and FPGAs (ReConFig). IEEE, 2017.

[12].Kurth, Andreas, et al. "HERO: Heterogeneous embedded research platform for exploring RISC-V manycore accelerators on FPGA." arXiv preprint arXiv:1712.06497 (2017).

[13].Zong, Ziliang, Rong Ge, and Qijun Gu. "Marcher: A heterogeneous system supporting energy-aware high performance computing and big data analytics." Big data research 8 (2017): 27-38.

[14].Giefers, Heiner, et al. "Analyzing the energy-efficiency of sparse matrix multiplication on heterogeneous systems: A comparative study of GPU, Xeon Phi and FPGA." 2016 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). IEEE, 2016.

[15]. Kotselidis, Christos, et al. "Heterogeneous managed runtime systems: A computer vision case study." Proceedings of the 13th ACM SIGPLAN/SIGOPS International Conference on Virtual Execution Environments. 2017.